开始之前

Q:为什么设计电路时候会用到二极管

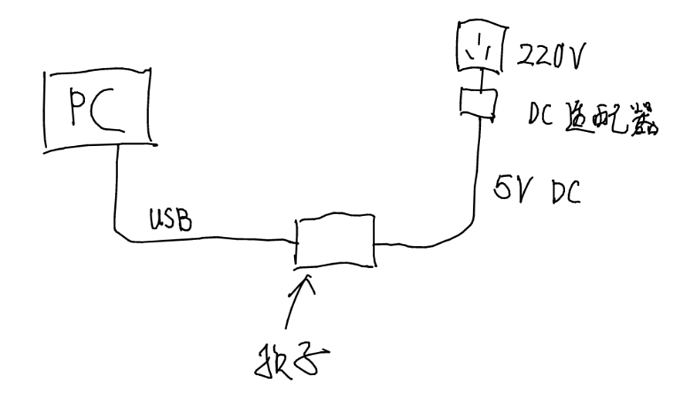

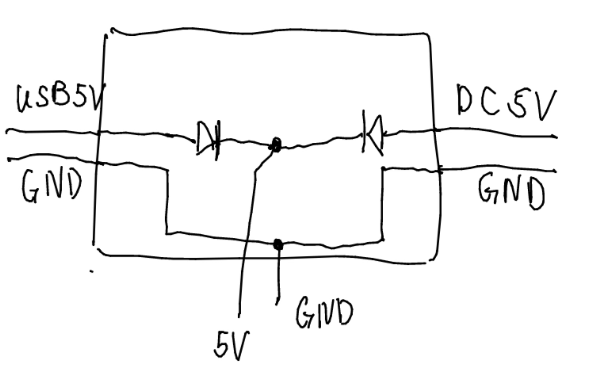

设计板子的供电电路时,经常会出现多电源的情况,比如电池/外部dc输入与来自USB的5V电源同时存在的情况:

对于GND来说很好处理,一般直接接一起是没事的,但是对于VCC(5V)来说,不能将USB来的5V和DC输入的5V直接并到一起,原因在于:

- 两边的5V永远不可能精确的相等

- 使电流从高一点的5V流去低一点的5V,浪费能量

- 有可能因为电流过大使得高一点的5V过载发热

- 以及低一点的5V可能设计上根本不能接受灌电流而直接损毁(比如烧主板)

所以需求就是阻止电流倒着灌进电源。阻止反向电流,直接能想到的就是二极管(Diode):

通过在两路电源输出位置分别接个二极管,阻止任何可能的倒灌电流。

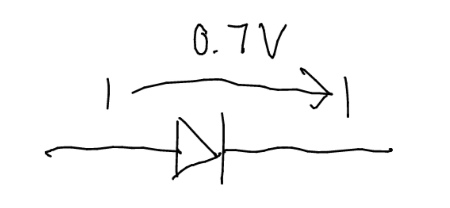

但是二极管是有极限的。为了使二极管导通,必须正向施加一个电压(通常是0.7V,PN结特性)。

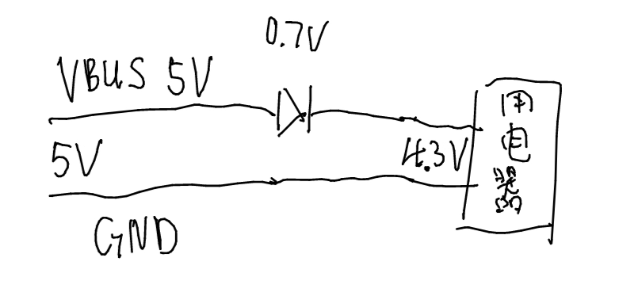

一般的应用场景足以提供这个导通电压,比如USB VBUS就是默认5V所以问题并不在于如何满足0.7V电压。但是,这个0.7V在电路运作中一直存在,也就是说,如果在USB VBUS上串了一个二极管防倒流,那么实际最高只能拿到4.3V的电压:

这就导致了功耗的问题。如果用电器需要2A的电流运转(10W),那么根据 P=UI ,在二极管上将产生至少1.4W的热功耗,产生的发热是不能接受的。

为了尽可能降低导通电压带来的问题,理想二极管(零压降二极管、Zero Voltage Drop)的设计被引入。

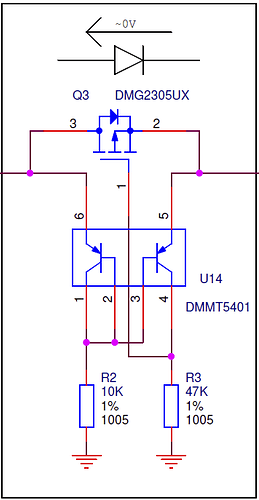

典型ZVD电路

下图为来自树莓派官方的ZVD推荐设计,用于各种树莓派兼容的扩展板中:

原始连接: hats/zvd-circuit.png at master · raspberrypi/hats · GitHub

可以看出,这个ZVD设计选用了一颗PMOS来承载电流,选用了两只PNP对MOS进行控制。两只PMOS在该电路中被集成到一起成为一个IC芯片。

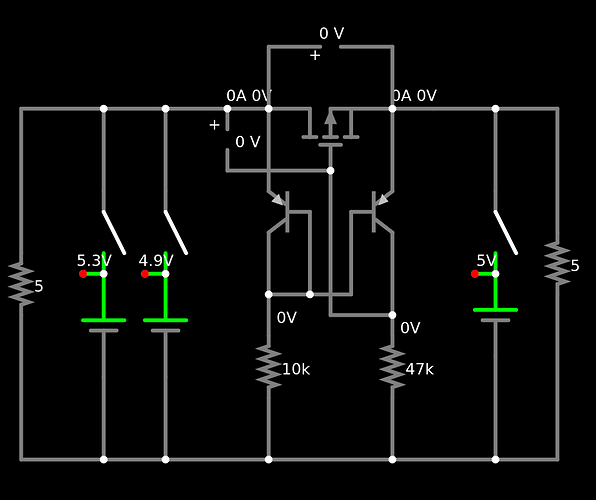

依照这份原理图,画一个仿真电路:

我在前一份原理图的基础上,加入了三个不同电压的电压源(模拟时候能提供无限电流大小)和左右两端的用电器(来使MOS管经过的电流可以被观测到)。通过在MOS管DS与GS间分别挂一个电压表来展示MOS不同的工作状态。额外的,根据 http://www.falstad.com/circuit/mosfet-beta.html 描述,我将MOS管的beta值调整到了80,作为功率管使用。

此处要求已大致了解MOS与BJT的basics,如果看了不知道在说啥,就去递归学习。

粗略认知

目标是构造一个零压降二极管,该方案使用一颗PMOS来通过电流。在MOS关断时,MOS的体二极管由左指向右,从而反向(从右向左)的电流默认状态下不会被放行。而从左向右的电流会经由体二极管放行,付出0.7V的PN结代价。而当打开MOS管后,电流可以绕开体二极管通过MOS,从而实现低开启内阻。但是,核心问题在于:MOS管开通之后,电流可以自由流动,无论是左到右还是右到左,所以增加的两颗PNP BJT则是为了控制在恰当的时机,打开和关闭MOS。

电路现象

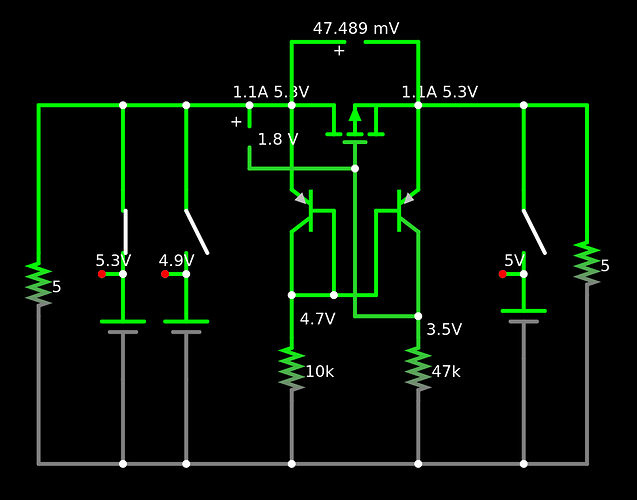

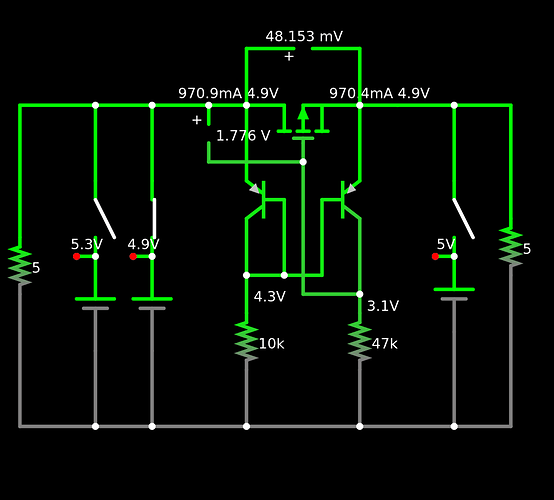

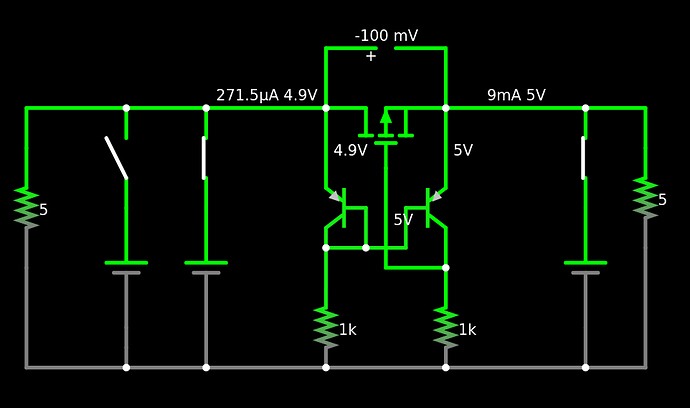

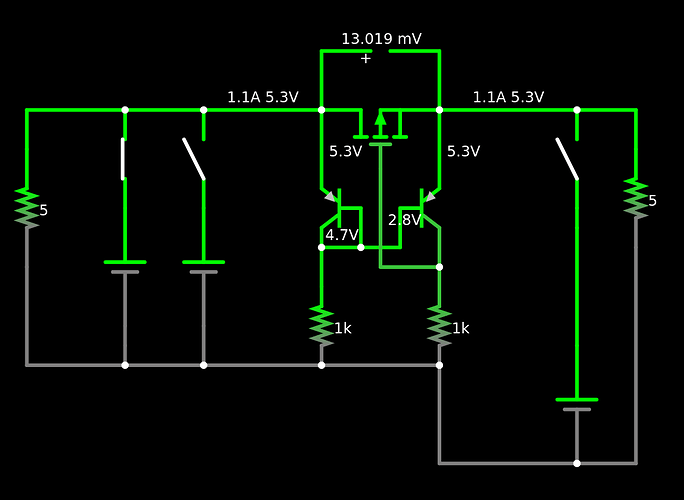

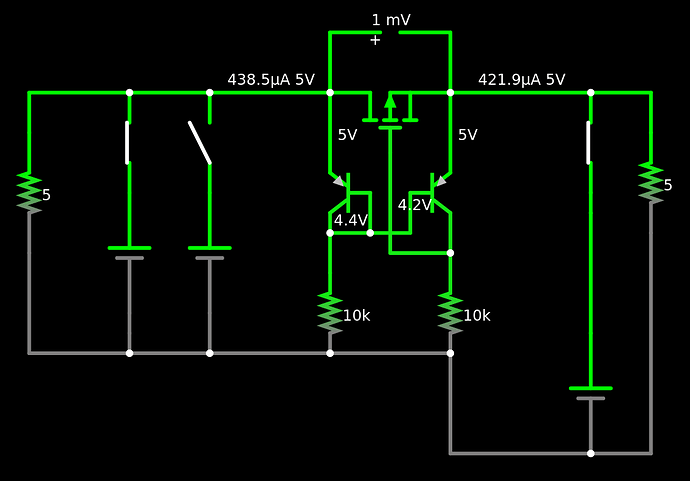

首先打开5.3V的开关:

DS间电压为47.4mV,表明MOS已经打开,此时GS电压1.8V(仿真时MOS管的开通电压设置在了1.5V)。左侧的5.3V电源对右侧的5欧姆电阻供电,MOS上通过了1.1A电流。

关闭5.3V开关,再打开4.9V开关:

可以看到,MOS依旧处于打开状态,保持较低的导通内阻。

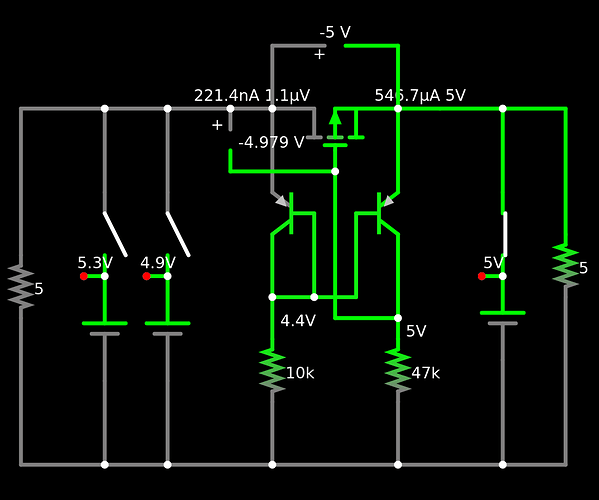

再关闭4.9V开关,打开右侧的5V开关:

此时发现电路状态产生明显变化。MOS两端出现-5V电压,且只有微弱的221nA电流通过,此时左侧的电阻上几乎没有电压,也就没有用电器电流,MOS处于关断状态。

定性分析

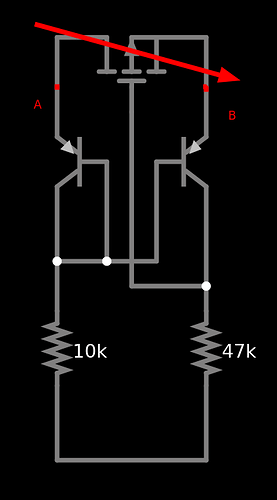

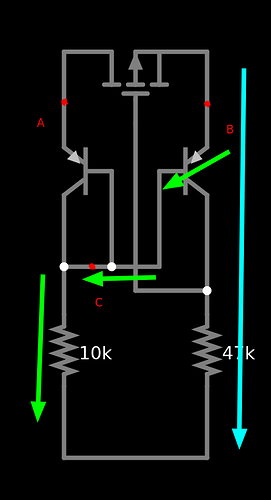

首先从电路没有电流开始,将左侧某一开关打开。在体二极管作用下,A点电压高于B点。

使得A点可以向C点产生电流,而电压较低的B点则无法向C提供电流。

C点通过10K电阻将电流导入回路中。

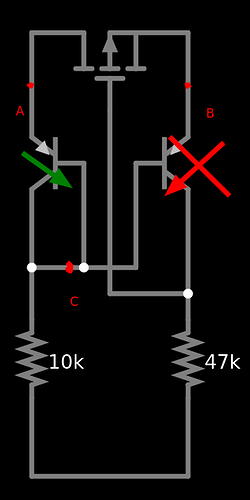

左边的BJT由于存在Collector-Base电流,使得晶体管产生Collector-Emitter放大电流,最终使得C点电压与A点接近。而右侧的BJT由于Collector-Base无法产生电流,因此处于“关断”状态,使得PMOS的Gate极电位被47K电阻下拉至接近0V(粗略的仿真中是3.5V/3.1V)。电路因而能实现正向导通PMOS,产生较低的导通电阻。

再分析右侧开关打开时的情况:

由于MOS管的体二极管,以及左侧BJT的PN结方向作用,电流几乎无法从右侧流向左侧,使得B点电压显著高于A点。同时,右侧BJT出现Collector-Base电流,在Collector-Emitter产生电流放大效应,使得电流由B点流向47k电阻,将PMOS的Gate脚拉至接近B点电压。此时,PMOS的DG间出现负压,而PMOS只在DG有足够正压时打开,因此此刻PMOS处于关断状态,没有电流可以逆流。

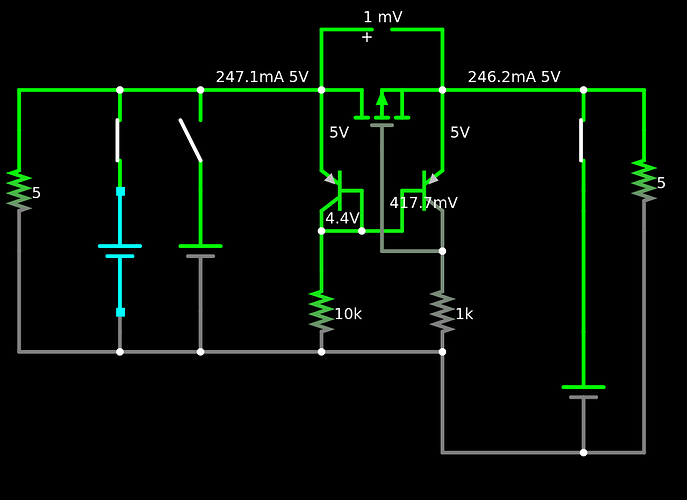

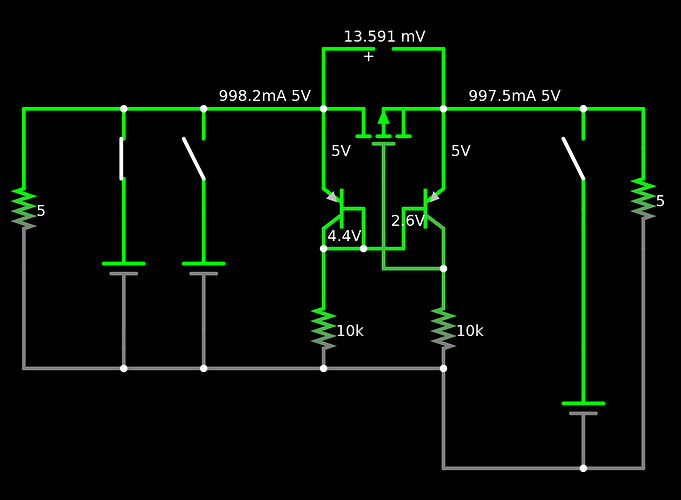

再来看一个特殊情况:

此时同时打开了左侧的4.9V与右侧的5V,也就是真实场景下双电源,其中左侧的电压较低的情况。左侧导线电流示数为271uA,是个相对较小的值,代表没有电流经过MOS管逆流。MOS管两端的电压则是双电源之间的压差。

另一个特殊情况:

此图做了稍许电路修改,限制了可以通过右侧电压源的电流大小。该图则是真实场景下右侧电压较低的情况,其中右侧的电压源没有灌电流保护。如若不加那颗电阻限制电流,则会灌出很高的电流来,以至于仿真失败。此时,MOS管仍能正常开通,用电器的电流仍由电压较高的左侧电压源提供。

上述两种特殊情况仍能正常工作的核心原因在于:BJT是流控器件,而很小的电压差就能提供引起BJT放大效应所需的C-B电流

定量应用

PMOS Vgs 极限值

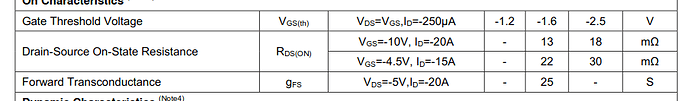

上述已经提及了,GS运行时会产生负压,其压差最大为右侧所能提供的电压。以NCE30P30K为例,数据手册中描述最大Vgs为

也就是说如果右侧电压高过20V,管子工作在关闭状态,Vgs>20V,就会裂开。当然左侧超了20V也可能会裂开,如果三极管能满足使管子Vgs<-20V。所以Vgs决定了PMOS在该电路中可以安全使用使的门限电压。(其它耐压参数一般都比这个高,不易满足)

可以通过分压电阻的形式来扩大支持的电压范围。

PMOS Rdon

在Vgs不同(温度也会影响)时,管子的导通电阻是不同的,这张图标记出的则是管子最棒的参数。个位数毫欧的导通内阻,无疑会降低压差与热功耗。

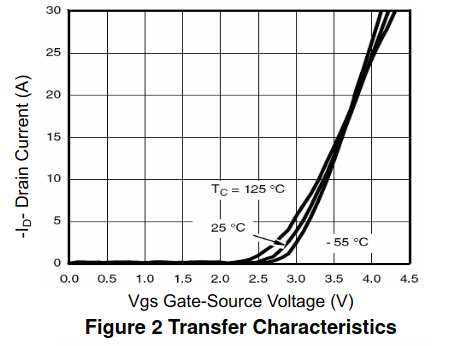

PMOS Vgs 开通界限

选型MOS的时候一定少不了这张图,它可以明确说明PMOS在不同的Vgs下的开关状态。比如这里基本可以断言,只要把Vgs控制在-2V以下,也就是S比G高2V以内,就可以保证管子关断,而做到-3.5V以外则可以提供足够小的开通电阻,满足使用需求。

PNP BJT选型与那两颗限流电阻

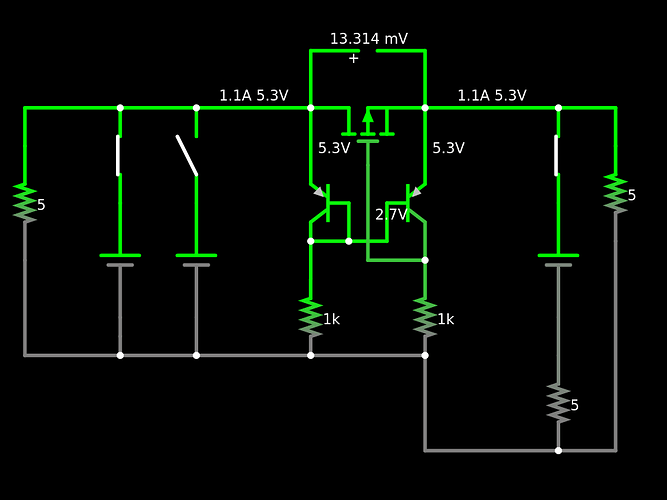

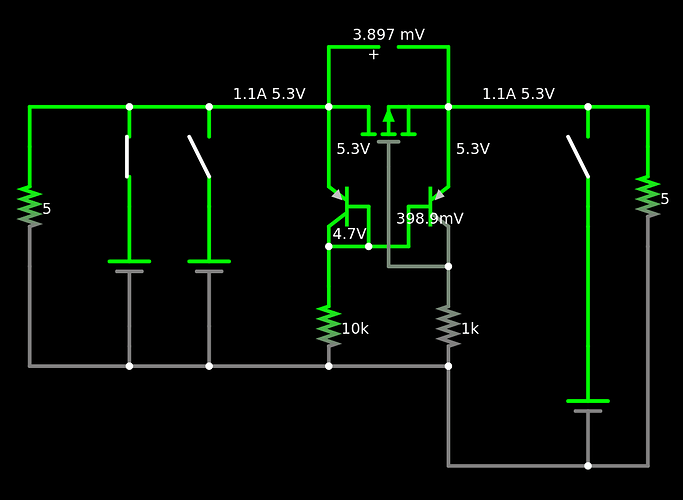

这里直接提供模拟电路图:

初识放置了两颗1k电阻。可以看到开启左边开关后,PMOS Gate电压离0V较远,说明右侧BJT并没有严丝合缝的关上。原因是:左侧的1k电阻太小,导致左侧BJT电流并不能很好的抑制右侧BJT放大。更换右侧的BJT,选择需要更大CE电流的管子可以改善,直接换个10k电阻也可以改善。

当然凡事都有代价。

将左侧电源换到5.001V后,反向漏电流产生了,还很大。用1k电阻时则漏的少一些,看图的绿色差异就能发现,10k时,右侧BJT的CB电流太小,不足以产生足够的放大效应,使得本该被拉高的PMOS Gate极没有被拉高。

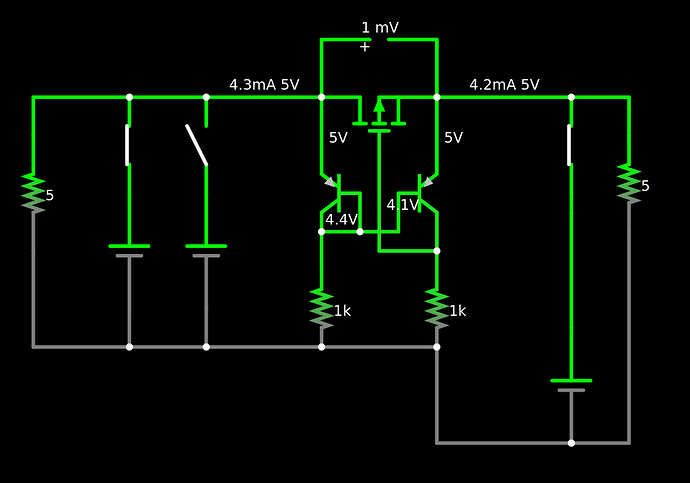

这时候小天才可能会想到,那就把右侧也换成10k吧:

确实,漏电流改善了,但是我们再换个工作状态:

发现Vgs又变回去了…导致的后果就是MOS不能完全导通,导通电阻增大。

所以说魔法电路真是…

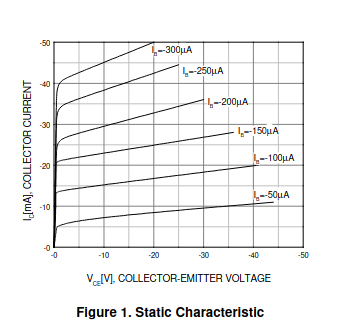

再补充一下BJT的数据手册使用方法。一般人就看这张:

重点关注Ib和Ic的关系,即电流的放大关系。用这张图来参考决定那俩根电阻的取值。

结语

盘算半天不如直接搭个电路试试来得快